MCU

汽车

快速排序

测试用例

JUC

Tableau

web大作业

大数据毕业设计

aws

chatgpt

知识产权

天气App

汇编大作业设计

微信公众平台

模板方法模式

语法格式

天气数据分析

自动控制原理

Firebase

linear regression

时序分析

2024/4/11 22:14:46FPGA时序分析与约束(5)——时序路径

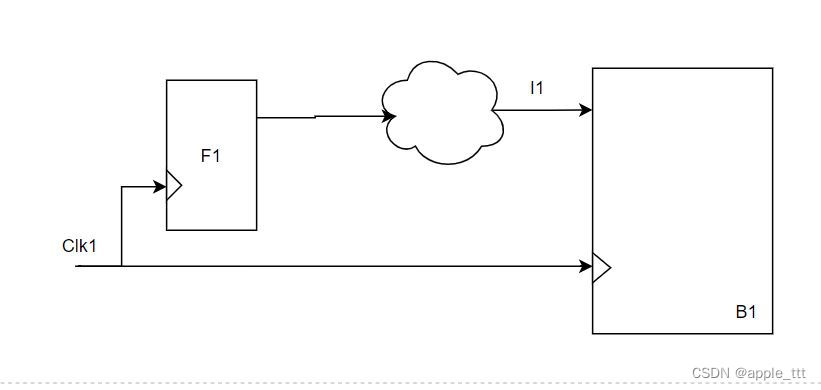

一、前言 在之前的文章中我们分别介绍了组合电路的时序,时序电路的时序和时钟的时序问题,我们也对于时序分析,时序约束和时序收敛几个基本概念进行了区分,在这篇文章中,我们将介绍时序约束相关的最后一部分基本概念&am…

FPGA设计时序约束十三、Set_Data_Check

目录

一、序言

二、Set Data Check

2.1 基本概念

2.2 设置界面

2.3 命令语法

三、工程示例

3.1 工程代码

3.2 约束设置

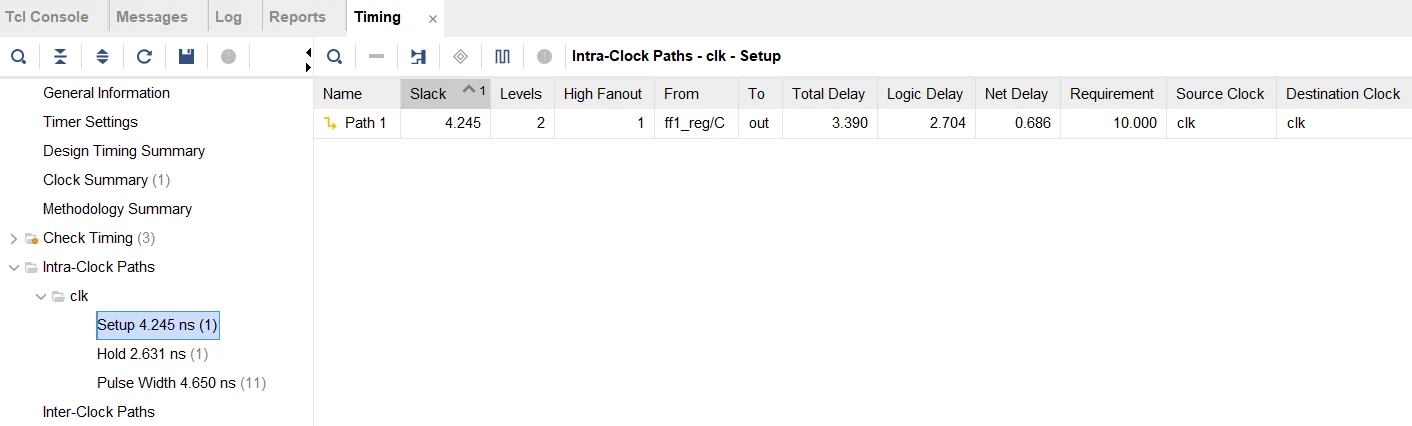

3.3 时序报告

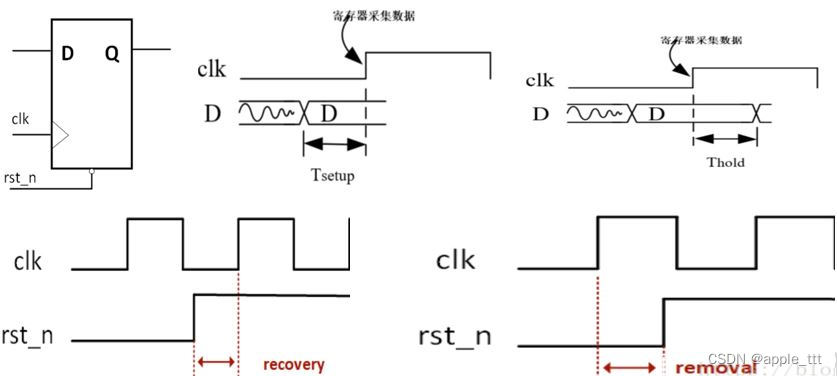

四、参考资料 一、序言 通常进行时序分析时,会考虑触发器上时钟信号与数据信号到达的先后关系,从而进行setu…

FPGA时序分析与约束(14)——虚拟路径

一、概述 到目前为止,我们已经看到了如何约束时钟和端口来指定设计中的时序要求,我们可以通过这些基础的约束命令来进行时序约束,但是时序分析工具默认的时序检查方式可能和我们实际工程实现的情况不同,通常来说是约束过紧&#x…

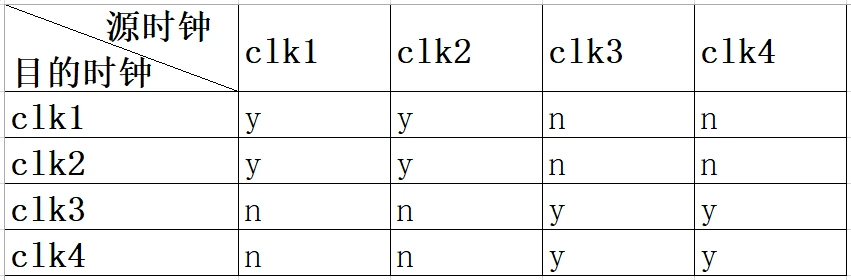

FPGA设计时序约束三、设置时钟组set_clock_groups

目录 一、背景

二、时钟间关系

2.1 时钟关系分类

2.2 时钟关系查看

三、异步时钟组

3.1 优先级

3.2 使用格式

3.3 asynchronous和exclusive

3.4 结果示例

四、参考资料 一、背景 Vivado中时序分析工具默认会分析设计中所有时钟相关的时序路径,除非时序约束…

FPGA时序分析与约束(3)——时钟不确定性

一、前言 在之前的文章中,我们介绍了组合电路的时序和时序电路的时序问题,在阅读本文章之前,强烈推荐先阅读完本系列之前的文章,因为这是我们继续学习的理论的理论基础,前文链接:

FPGA时序分析与约束&…

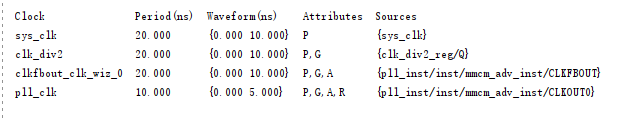

基于Xlinx的时序分析与约束(5)----衍生时钟约束

衍生时钟约束语法 衍生时钟(Generated Clocks,又称为生成时钟)是指由设计中已有的主时钟通过倍频、分频或者相移等操作后产生的新的时钟信号,如由MMCM或PLL或由组合逻辑生成的倍、分频时钟信号。 衍生时钟约束必须指定时钟源&…

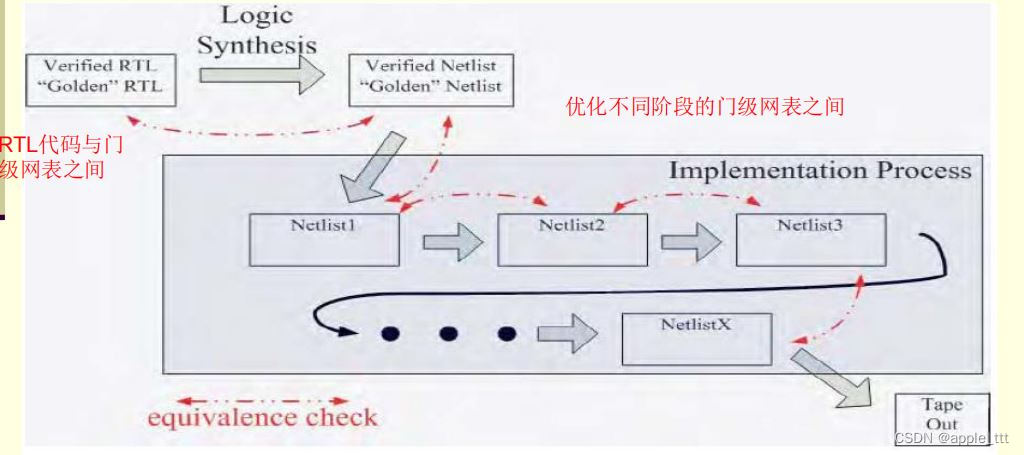

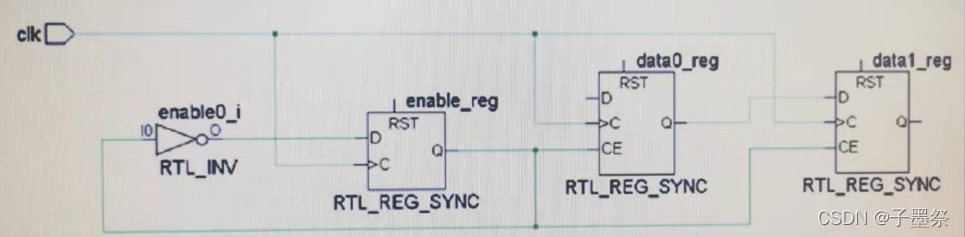

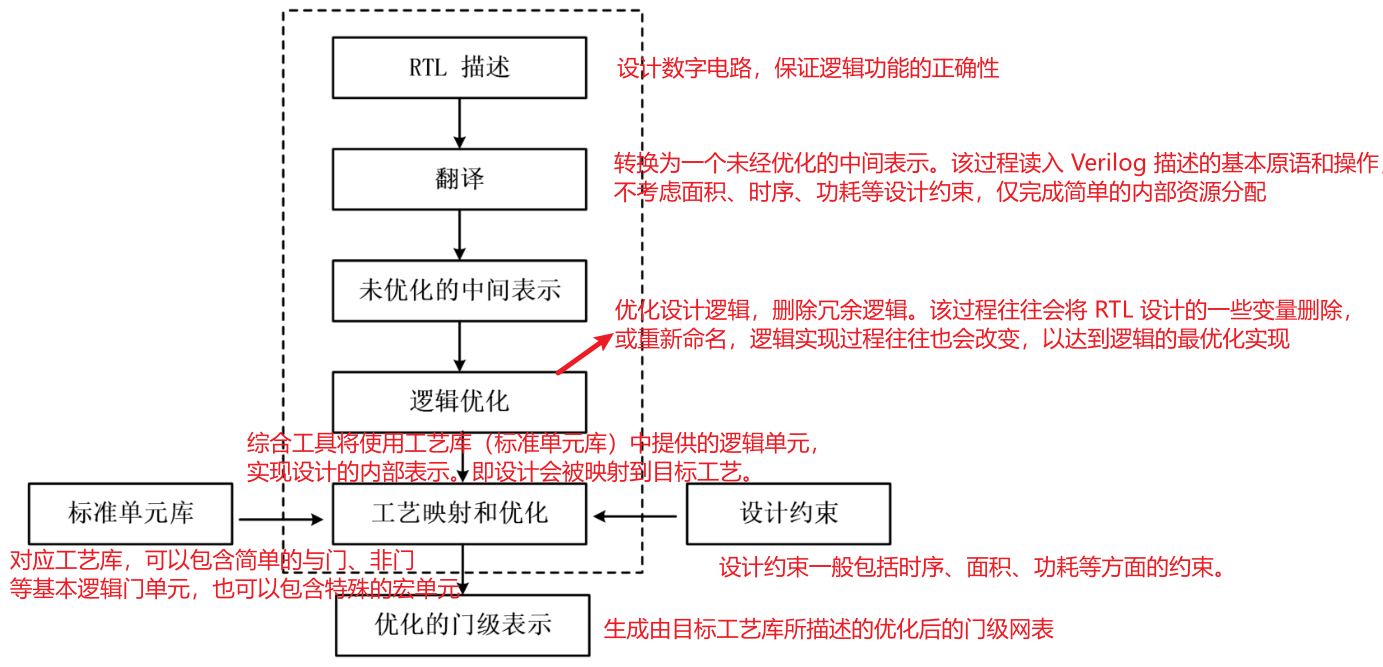

仿真验证方法(2)——静态验证

一、静态验证

1.1 概述 在之前的文章中,我们介绍了动态仿真,但是动态仿真用于百万门以上电路时所需时间极长,而且其功能覆盖率取决于所设计的输入激励向量,很难达到100%,因此静态时序分析和等效性检查这样的静态验证是…

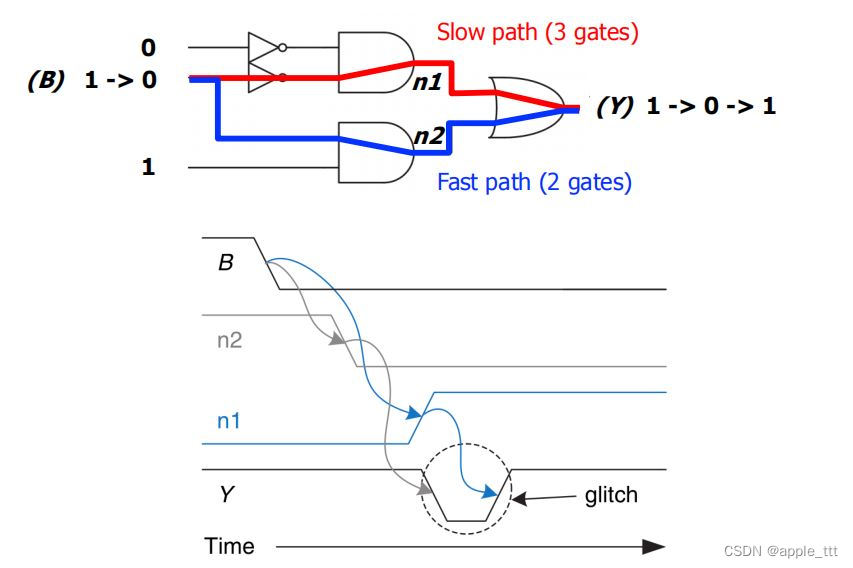

FPGA时序分析与约束(1)——组合电路时序

写在最前面: 关于时序分析和约束的学习似乎是学习FPGA的一道分水岭,似乎只有理解了时序约束才能算是真正入门了FPGA,对于FPGA从业者或者未来想要从事FPGA开发的工程师来说,时序约束可以说是一道躲不过去的坎,所以从这篇…

FPGA时序分析与时序约束(一)

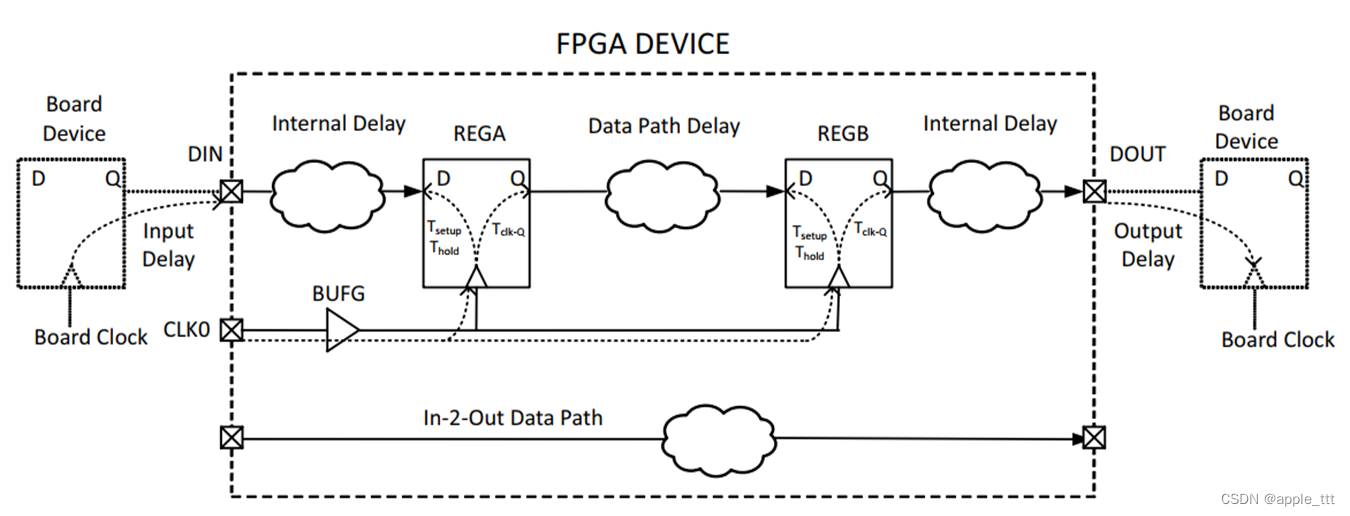

一、为什么要进行时序分析和时序约束 PCB通过导线将具有相关电气特性的信号相连接,这些电气信号在PCB上进行走线传输时会产生一定的传播延时。 而FPGA内部也有着非常丰富的可配置的布线资源,能够让位于不同位置的逻辑资源块、时钟处理单元、BLOCK RAM、D…

【FPGA】时序概念

目录

一、时钟定义

1.1 Primary Clocks

1.2 Generated Clocks

1.3 Virtual Clock

1.4 Clock groups

二、时钟分类

三、I/O delay约束

四、Timing Exception 一、时钟定义

Primary ClockVirtual ClockGenerated ClockClock groups1.1 Primary Clocks

…

FPGA时序分析与时序约束(二)——时钟约束

目录

一、时序约束的步骤

二、时序网表和路径

2.1 时序网表

2.2 时序路径

三、时序约束的方式

三、时钟约束

3.1 主时钟约束

3.2 虚拟时钟约束

3.3 衍生时钟约束

3.4 时钟组约束

3.5 时钟特性约束

3.6 时钟延时约束 一、时序约束的步骤 上一章了解了时序分析和约束…

Verilog学习记录

目录

一、Verilog简介

(一)Verilog 的主要特性

(二)Verilog的主要应用

(三)Verilog设计方法

二、Verilog基础语法

(一)标识符和关键字

(二)Verilog数据…

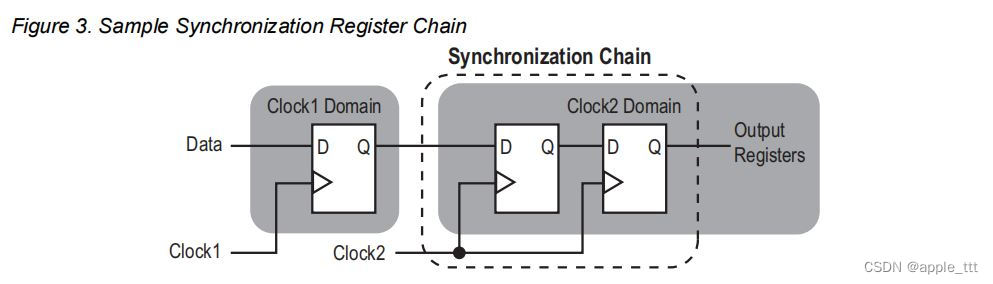

理解FPGA中的亚稳态

一、前言 大家应该经常能听说到亚稳态这个词,亚稳态主要是指触发器的输出在一段时间内不能达到一个确定的状态,过了这段时间触发器的输出随机选择输出0/1,这是我们在设计时需要避免的。本文主要讲述了FPGA中的亚稳态问题,可以帮助…

FPGA时序分析与约束(4)——时序分析,时序约束,时序收敛

一、前言 在之前的文章中,我们介绍了组合电路的时序和时序电路的时序问题,之后又把理想化的时钟变成了实际的时钟考虑了进来,在阅读本文之前,强烈推荐优先阅读本系列之前的文章,毕竟这是我们继续学习的基础,…

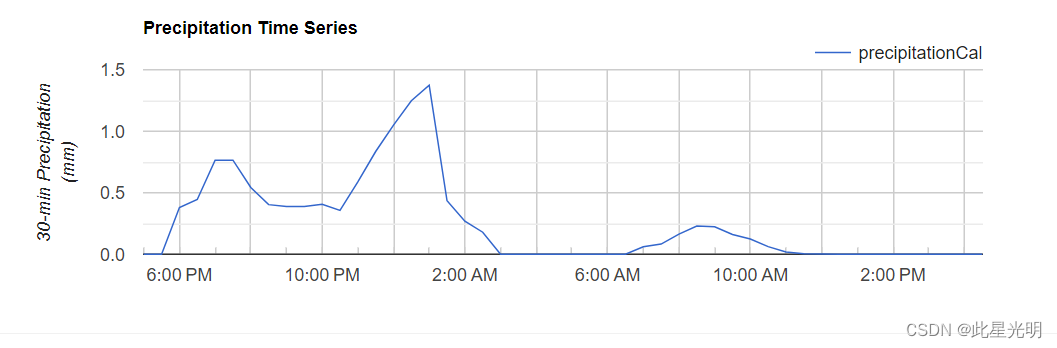

GEE——降水数据分析(半天)图表分析含(IANA(IANA Time Zone Database) 时区名称的定义)

简介

我们在进行某个时间的降水数据分析的时候,或者指定时间的数据分析,本文我们首先要明确一点就是我们可以设定时间,除了默认的时间外,我们可以选择归一化的时间,也可以选择全球任何一个时区的时间作为时间设定。

…

FPGA时序分析与约束(13)——I/O接口约束

一、概述 在应用了时钟约束后,所有寄存器到寄存器的路径都能定时。为了获得更加精准的FPGA外部时序信息,设计者需要为FPGA的I/O接口指定时序信息,一般时序工具只能获取FPGA器件内部的时序信息,对于FPGA器件引脚之外的时序信息&…

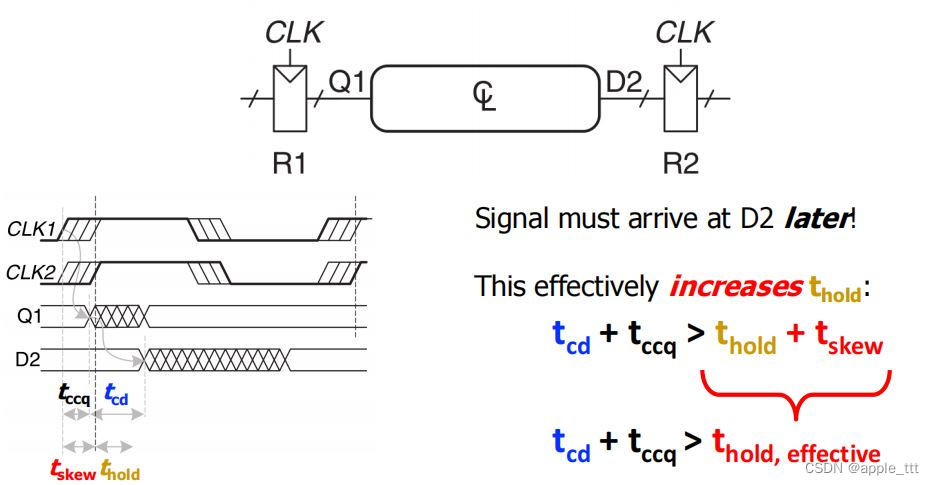

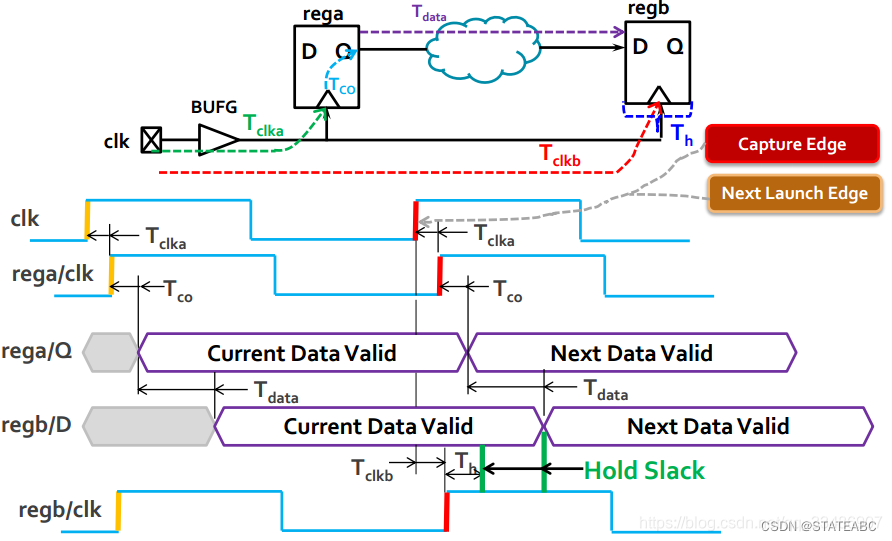

静态时序分析中的计算问题

1. 几个重要概念

1.1 Clock Setup Time (Tsu)

时钟沿到来之前数据需要稳定的时间 1.2 Clock Hold Time (Th)

时钟沿到来之后数据需要稳定的时间 1.3 Clock-to-Output Delay(Tco)

寄存器的时钟有效沿 —— 》寄存器Q端有输出的时间

1.4 Clock skew

…

FPGA时序分析与约束(0)——目录与传送门

一、简介 关于时序分析和约束的学习似乎是学习FPGA的一道分水岭,似乎只有理解了时序约束才能算是真正入门了FPGA,对于FPGA从业者或者未来想要从事FPGA开发的工程师来说,时序约束可以说是一道躲不过去的坎,所以这个系列我们会详细介…

GEE生物量碳储量——利用sens和MK检验方法计算1987-2022年森林地上生物量AGB和碳储量的时空变化特征

简介:

本文是将之前已经处理好的森林生物量和碳储量数据保存到GEE Assets中,然后分别将单张影像导入到代码编辑器中,构建一个时间序列集合,并且这里需要用到的是我们给影像添加指定的时间属性,这样方便进行下一步的时序分析和空间预测。

首先,需要收集1987年至2022年期…